# 小型高出力車載充電器の開発

Development of Small-Size, High-Power Output On-Board Charger

望 月 賢 人

Kento Mochizuki

冨 永 麗 司 Reiji Tominaga

湊 純 司 Jyunji Minato 中 井 久 史 Hisashi Nakai

#### 要旨

EV/PHEVに求められる小型・高出力車載充電器として、業界最高レベルとなる電力密度1.3 kW/L,最大効率95%の車載充電器を開発した。高出力化のために回路規模が大きくなるという従来課題を解決し、出力電力を維持しつつ小型化を実現した。小型化のポイントは大きく2点ある。1つ目は3.3 kW出力の2並列構成を6.6 kW出力シングル構成に集約し、回路規模を半分に削減したことである。2つ目はトランスの漏れインダクタンスのばらつきを管理する技術を実現することで、MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)の低損失スイッチング実現のために必要な共振コイルを削減し、トランスやコイルの占める体積を低減したことである。これにより、従来の0.5 kW/Lから2倍以上の電力密度向上に貢献した。本技術は、軽量化によるEV/PHEVの電費改善にも寄与する。

#### Abstract

A small-sized, high power output on-board charger has been developed for Electric Vehicles and Plug-in Hybrid Electric Vehicles (EV/PHEV) with a power density of 1.3 kW/L and efficiency of 95 %. High power density was achieved without reducing the power output by solving the problem of a trade-off between high power output and large circuit size. There were two main points to tackle in order to realize a small-sized on-board charger. First, the circuit size was halved by realizing a 6.6 kW single-circuit structure from the conventional 3.3 kW parallel circuit. Second, a resonant coil for Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) soft switching was eliminated by developing a new transformer that incorporates a resonant coil function by adjusting the leakage inductance. Through these approaches, the power density was improved to more than two times the conventional product at 0.5 kW/L. This development also contributes to reducing the weight of EV/PHEV and improves the driving distance.

## 1. はじめに

EV (Electric Vehicle) /PHEV (Plug-in Hybrid Electric Vehicle) は、電池に蓄えられた電力を動力源とした電動 走行が可能な車両であり、近年急速に普及が進んでいる。 EV/PHEVに搭載される電池は、長距離の電動走行を実現 するために容量が大きく、車外の外部電源からの充電が必要となる。そのため、家庭用コンセント (AC85 V~264 V) から電池を充電するための装置として車載充電器を搭載している.

車載充電器に求められる要件として、EVでは航続距離を長くするために大容量の電池を搭載する必要があり、電池をより短時間で充電するために、大電力であることが求められている。また、PHEVでは内燃機関(エンジン)と電動モータの2つの動力源を搭載しており、車室・荷室空間を広く確保するため、小型であることが求められている[1].

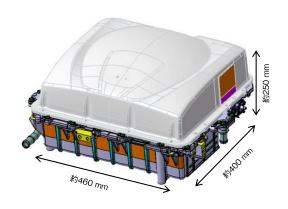

当社はすでに2012年にEV用の車載充電器として,世界初となる6.6 kW出力を実現,電力密度0.5 kW/L・最大効率92%に達する車載充電器を開発し,日産自動車(株)製リーフ(注)への搭載を果たしている.第1図は量産中

(注1) リーフおよびleafは日産自動車(株)の登録商標または 商標.

## の車載充電器の外観である.

車載充電器における一般的な課題は、高出力にすることによって、サイズが大きくなることである。本稿では、新規回路検討とトランス開発によって、このトレードオフ問題を克服し、車載充電器の小型・高出力化を実現したので、その技術内容を紹介する。

第1図 量産中の車載充電器外観

Fig. 1 Isometric view of on-board charger under mass production

# 2. 従来技術と課題

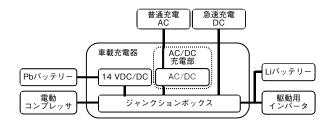

リーフ用に開発した車載充電器のブロック図を**第2図**に示す. 6.6 kW出力可能なAC/DC充電部に加え,車載LiバッテリーからPbバッテリーを充電する14 VDC/DCコンバータ部,急速充電スタンドからのDC400 Vを入力して電動コンプレッサ部へ電力供給を行う,ジャンクションボックスを1つの筐体(きょうたい)内に一体化した構成となっている. このため28 Lとサイズが大きく,そのなかでもAC/DC充電部は13 L程度の体積を占める.

第2図 車載充電器のブロック図

Fig. 2 Block diagram of on-board charger

#### 2.1 従来回路構成

AC/DC充電部の回路を構成する部品には最大30 A以上の大電流が流れるため導通損失が大きくなる。したがって、6.6 kW出力を実現するため、電流量を分散させる必要があり以下の回路構成を採用した。

#### 〔1〕 MOSFETの並列駆動

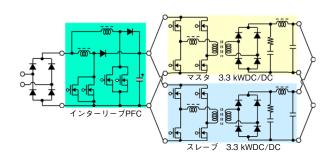

第3図に並列回路構成におけるAC/DC充電部の回路図を示す。PFC(Power factor correction)回路とフルブリッジDC/DC回路から構成される。PFC回路は伝導ノイズと損失による発熱を抑制させるため、インターリーブ回路[2]を採用し、MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)を2並列にする構成とした。この場合、MOSFETがONとなるタイミングのばらつきにより一方のMOSFETに電流が集中し、定格損失超過による発熱や、寄生成分の影響による発振により破壊する懸念がある。そこで、基板配線パターンの寄生インダクタンスを考慮した等長配線、ノイズを抑制するフェライトビーズの挿入により、ばらつきの影響を抑え、安定したスイッチング特性を実現した。

# 〔2〕DC/DC並列回路制御

第3図に示すようにDC/DC部は、フルブリッジ回路を各3.3 kWの出力からなるマスタ/スレーブの2段構成とすることで6.6 kW出力に対応した。出力電力の制御は、マスタの出力電流のみをフィードバックに使用し、マスタへの指令値を同時にスレーブへ伝達する電流制御とし、

各回路の独立制御に比べシンプルな制御を行った.

第3図 並列回路構成図

Fig. 3 Circuit diagram of parallel circuit configuration

## 2.2 小型化への課題

上記により、6.6 kW出力を実現したが、PFC回路部のMOSFETを並列構成にし、フルブリッジ回路部を3.3 kW回路×2段の並列構成しているため、回路規模が大きい。同時に、MOSFETの安定したスイッチングを行うための追加回路や、マスタ/スレーブ回路の同期化のための制御回路も回路サイズを大きくする要因である。

また、フルブリッジ回路部に使用しているトランスは、 回路を構成する部品のなかで最も大きく、さらに、ソフトスイッチングに必要な共振コイルを個別部品として直 列に接続しているため、回路全体の面積のうち1/5程度を 占めている.

以上から、小型化するためには回路規模の削減と、トランスやコイルなど磁気部品の体積削減が有効である. 以下にこれら小型化へのアプローチについて述べる.

## 3. 小型化技術

## 3.1 シングル回路方式による回路規模削減

小型化実現のために,前節で述べた並列回路構成をシングル回路構成とする検討を行った.

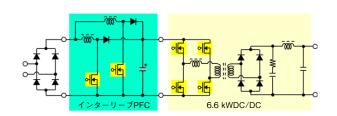

第4図に、シングル回路構成におけるAC/DC充電部の回路図を示す。3.3 kW回路×2段の並列構成から6.6 kW×1段のシングル回路構成とし、また、PFCに並列で使用し

第4図 シングル回路構成図

Fig. 4 Circuit diagram of single-circuit configuration

ているMOSFETを1つにすることで、回路面積を2/3に縮小することができる.

## 〔1〕シミュレーションによるMOSFET低損失化検討

シングル回路構成に変更した場合、PFC部およびDC/DC部どちらのMOSFETも1素子あたり最大8 Aから16 Aへ電流量を増やす必要がある. 導通損失を下げるために低ON抵抗であるSJ (Super Junction) MOSFETを採用した. MOSFETの変更により、寄生容量が大きくなることで、スイッチング特性変化による損失の増加が課題となる. この課題解決のため、シミュレーションを用いて周辺定数の検討を行った.

従来は、シミュレーションモデルのパラメータ作成に 制約があったため、半導体の寄生成分を考慮したモデル パラメータの見極めができていなかった。このため、シ ミュレーション上でスイッチング時のサージなど、正確 に再現することが困難であった。

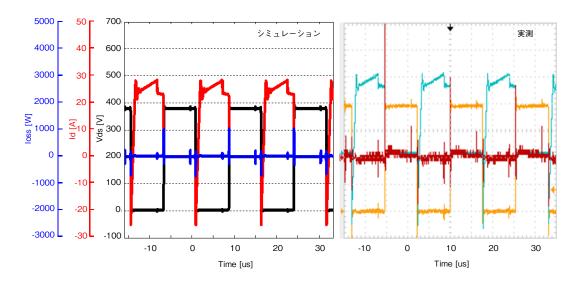

今回, 半導体の寄生成分を実測から高精度にモデリングすることによって, 実測と同等な波形確認が可能となった. 第5図に6.6 kW動作時のシミュレーションと実測波形の比較結果を示す. トランスの電流および電圧波形と, それらから算出した損失波形である. 損失波形の時間平均は, MOSFET 1つあたり23 W程度であり, PFC部とともに部品定格温度以下となることを確認した.

実測とシミュレーションの相関が取れることにより, ゲート抵抗やデッドタイムの調整を容易に行うことが可 能となった.

# [2] SJMOSFET用駆動回路設計

MOSFETの変更によって、ゲート容量であるQgが増加

する. 従来のHVIC(High Voltage IC)では、内部の抵抗成分が数 $\Omega$ 台と大きく、ゲート駆動能力が足りない。そこで、フォトカプラ方式の駆動回路に変更することにより、内部抵抗成分を数 $100~m\Omega$ 台に低減し、Qgが増加した場合でも安定したスイッチングを実現した。

さらに、ゲート駆動回路電源には回路規模の小型化のためにブートストラップ方式を採用している。ダイオードとコンデンサを利用して電力を供給しているため、Qgの増加に伴いダイオードの発熱が課題となっていた。そこで従来のダイオードから低Qrr(逆回復電荷)、低VF(電圧降下)のダイオードへ変更することにより発熱を抑制した。

第1表に以上の取り組みにより削除した主要デバイスの員数比較を示す. TO-247パッケージのパワーデバイスを8個削減し, 従来比約50%の面積を削減した.

第1表 主要デバイス員数の比較

Table 1 Comparison of the number of main devices

|        | 並列構成 | シングル構成 |

|--------|------|--------|

| トランス   | 2個   | 1個     |

| ダイオード  | 8個   | 4個     |

| MOSFET | 8個   | 4個     |

#### 3.2 新規トランス開発による部品点数削減

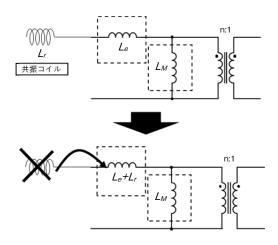

MOSFETの一般的なスイッチング損失の低減手法としてZVS(ゼロボルトスイッチング)があり、これを活用している[3]. LCの共振現象を利用しているため、トランスの励磁インダクタンスとは別に、直列に共振用インダクタンスが必要である。従来の回路方式では共振コイ

第5図 MOSFET時間応答波形の実測とシミュレーションとの比較

Fig. 5 Simulation result of MOSFET output response

ルを外付けしていたため回路サイズが大型化していた.

#### 〔1〕トランスの構造設計

共振コイルを含む、トランスの等価回路を**第6図**に示す。トランスにはリーケージインダクタンス(漏れインダクタンス)が存在し、このリーケージインダクタンス

$L_r$ : 共振用インダクタンス  $L_e$ : 1次漏れインダクタンス  $L_M$ : 励磁インダクタンス

第6図 リーケージインダクタンス内蔵トランスの等価回路 Fig. 6 Circuit of the transformer with adjusted leakage inductance

を小さく、結合度を高くすることが一般的なトランスである.

従来はトランスとは別に共振コイルを外付けし、インダクタンス値を調整していた。トランスがもつリーケージインダクタンスを共振用インダクタンスとして積極的に活用することにより外付けしていた共振コイル無しでもZVSが可能となり、小型化に貢献した。

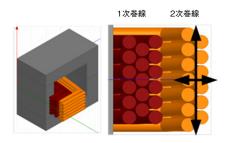

従来のトランス設計では、1次巻線と2次巻線を密接させた状態で交互に巻くことで高い結合度を得ていた。1次巻線と2次巻線の位置関係によってリーケージインダクタンス値が決まるが、巻線の位置関係のばらつきが大きく、リーケージインダクタンスのばらつきも大きいことが課題であった。これを解決するため、1次巻線と2次巻線との位置関係をボビン構造によって固定することにより結合度を一定に保った。第7図は、コア、1次巻線、2次巻線それぞれの位置関係を示している。2次巻線の位置を調整し、要求されるリーケージインダクタンスを実現した。コア材料の透磁率のばらつきが±30%であるため、共振コイルのインダクタンスのばらつきも±30%になるが、トランスのリーケージインダクタンスのばらつきは巻線の位置関係のみによって決まることを利用し、±10%以下のばらつきに抑えることが可能となった。

これにより、トランス単体で安定したZVSを実現し、

共振コイルの削除が可能となった.

第7図 リーケージインダクタンスの調整図 Fig. 7 Adjusting view of the leakage inductance

## 〔2〕トランスの損失低減

共振コイルをトランスへ内蔵させたことにより、リーケージインダクタンスに起因する損失が増加する。さらに、トランス自身の小型化も行っているため熱容量が小さくなることによる温度上昇が課題であった。これを解決するため損失を分散することによる発熱抑制を検討した。

トランスの損失は大きく分けて,

- ・磁性体コア損失による鉄損

- ・ 巻線の損失による銅損

の2つで構成される.トランスの負荷は,出力電圧最大時に磁束密度が大きくなるため鉄損が大きく,逆に出力電圧最小時に出力電流が最大となり銅損が大きくなる.このどちらの条件についても部品定格温度を満足しなければならない.

式 (1) は、トランスの磁束密度を求める式である. 小型化するデメリットとして、コア断面積 $A_e$ と巻線巻き数Nの低下により、磁束密度 $\Delta B$ が増加する[4].

$$\Delta B = \frac{L \times I}{A_e \times N} \qquad (1)$$

L: 励磁インダクタンス, I: 励磁電流

$A_e$ :コア断面積,N:巻き数

$$P_{CV} = a \times f^b \times \Delta B^c \qquad \cdots \qquad (2)$$

a, b, c: 材料によって決定される係数

式 (2) は、磁束密度から求める鉄損の算出式である。  $\Delta B$ が増加するため、 $P_{cr}$ も増加する.

以上から、小型にすることにより鉄損が増加することがわかる. 放熱構造の制約から鉄損は大きく、一方銅損は可能な限り小さくなるようバランスを調整した. 以下に鉄損と銅損の放熱方法について述べる.

# 〔3〕鉄損の放熱設計

本トランスの設計では、フルブリッジ回路であることと、車載環境(環境温度最大85 $^{\circ}$ )であることから、 $^{\circ}$

Bを最大磁東密度の50%程度となるよう設定した. 発熱をコア経由で放熱器に放熱可能な構造なため, トランス自身17 mmの低背化を行うことで, コアの放熱効率を向上させコアサイズを最小の巻き数比と実行断面積から, 巻線長を短く交流抵抗値が小さくなるよう設定し, 鉄損による発熱が積極的に大きくなる構造とした.

#### 〔4〕銅損の放熱設計

本トランスの構造は、巻線が放熱器と直接接する構造ではないため銅損の放熱方法が課題であった.コア側に1次巻線、外周に2次巻線が巻かれ、さらにリーケージインダクタンスのためのギャップが空いており、特に1次巻線の放熱経路確保が難しい。そこでトランスを放熱ケースに挿入し、そのケース内部に放熱樹脂を充填することにより放熱樹脂を介して放熱器へ放熱する構造を採用した。また、表皮効果低減のためリッツ線を用いており、リッツ線の直径と本数を周波数と交流抵抗値から設定し銅損が小さくなる構成とした。

以上により、トランスの体積を従来に比べ35%削減し、小型化による温度上昇を従来と同等に抑えることができた.

# 4. まとめ

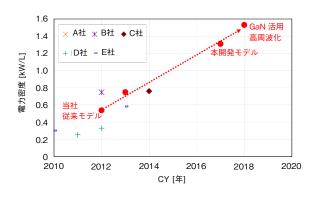

各パワーデバイスの削減と、回路方式の検討によって 回路規模の削減を行い、さらにトランスの新規開発により、部品点数削減および小型化を行った。これらにより、 電力密度1.3 kW/Lの小型高出力車載充電器を実現した.

第8図に他社も含めた車載充電器の電力密度を示す. 今後の取り組みとしては、GaN(窒化ガリウム)デバイスを活用することでスイッチング周波数の高周波化を行いさらなる小型化を目指す.これら小型化されたAC/DC充電部と、駆動用インバータなどと統合化していくことで顧客価値の創出につなげていく.

第8図 電力密度の推移と目標値

Fig. 8 Changes in power density and target value

## 参考文献

- [1] 吉田崇, "電気自動車 (EV) 用システムの課題と開発動向," パナソニック技報, vol. 57, no. 3, pp. 44-45, 2011.

- [2] 佐藤守男, "インターリーブ臨界モード4kW PFCの設計と試作," グリーン・エレクトロニクス no.3, pp. 91-92, 2010.

- [3] 稲葉保, "フェーズ・シフトPWM方式ZVS可変電源の製作," トランジスタ技術, 6月号, pp. 28-229, 2014.

- [4] 馬場清太郎, "インダクタとトランス," 電源回路設計成功 のかぎ, pp. 301-331, 2009.

# 執筆者紹介

望月 賢人 Kento Mochizuki オートモーティブ&インダストリアルシステム ズ社 車載エレクトロニクス事業部 Automotive Electronics Systems Business Div., Automotive & Industrial Systems Company

冨永 麗司 Reiji Tominaga オートモーティブ&インダストリアルシステム ズ社 オートモーティブ事業開発センター Automotive Business Development Center, Automotive & Industrial Systems Company

湊 純司 Jyunji Minatoオートモーティブ&インダストリアルシステムズ社 オートモーティブ事業開発センターAutomotive Business Development Center,Automotive & Industrial Systems Company

中井 久史 Hisashi Nakai オートモーティブ&インダストリアルシステム ズ社 車載エレクトロニクス事業部 Automotive Electronics Systems Business Div., Automotive & Industrial Systems Company