# 分散型バスにおける伝送負荷均一化方式

Load Equalization Methods for Distributed Buses

吉 田 篤 石 井 友 規 山 口 孝 雄 Atsushi Yoshida Tomoki Ishii Takao Yamaguchi

#### 要旨

本稿は、半導体集積回路内のバスにおいてトラヒック量の増大により、集中型バスのバス動作周波数が増大する課題に対し、分散型バスを用いてバス動作周波数を増大させることなく伝送帯域を増加させる伝送負荷均一化方式について述べる。本方式は、伝送を中継するノードの自律分散的な伝送負荷均一化処理により、バス全体の伝送負荷を均一に保ち、バス動作周波数の増大を抑制する。本方式をハードウェア実装し、4段のバタフライ網を対象とした評価で、スレーブ数が4個の場合に、バス動作周波数を増大させることなく平均スループットの最大値を3倍に向上できることを確認した。

#### Abstract

For the bus architecture of large-scale integrated circuits, there is a problem that increased amounts of traffic cause an increase in the frequency of the centralized bus. This paper describes a load-equalization method which can increase the transmission bandwidth without increasing the bus frequency on the distributed bus.

In order to suppress the rise in bus frequency, the method avoids traffic congestion using autonomous distributed control for load equalization at each node.

We implemented the load-equalization method on a distributed bus, and evaluated it in a 4-stage butterfly network with 4 slaves. The results showed that the maximum value of average throughput was improved to three times higher without increasing the bus frequency.

## 1. はじめに

近年、半導体集積回路の大規模化や高機能化に対し、ハードウェアの実装面積を抑えながら、伝送帯域を最大化できるバスの実現が求められる。しかし、クロスバ・スイッチに代表される集中型バスによる開発が困難になってきている[1]. その主な要因として、①バスマスタ(例えば、プロセッサやDSP:Digital Signal Processorなど)の配置制約、②バス配線の集中やバスの種類の多様化、③トラヒック量の増加によるバス動作周波数の増大などが挙げられる。

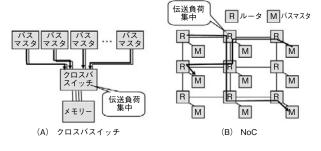

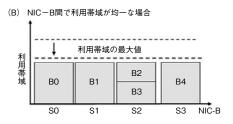

集中型バスでは、クロスバ・スイッチに伝送負荷が集中するため、バス動作周波数が増大しやすい(第1図(A)). 従来から、集中型バスの課題解決のためにバスをネットワーク化し、ルータを用いてパケット交換方式の通信を行うNoC(Network on Chip)の研究が行われている[1].

本稿では、分散型バスを用いてバス動作周波数を増大させることなく伝送帯域を増加させる方法について述べる。分散型バスの場合でも、トラヒックが相互に干渉することで、局所的な伝送負荷の集中が発生し、バス動作周波数が増大することがあるが(第1図(B))、伝送負荷集中を抑制できる伝送負荷均一化方式を用いることで、バス動作周波数の上昇を抑制する。

第1図 半導体集積回路内のバスでの伝送負荷集中

Fig. 1 Concentration of transmission loads in bus architecture of large scale integrated circuit

# ■ 2. NoC構造のメリット

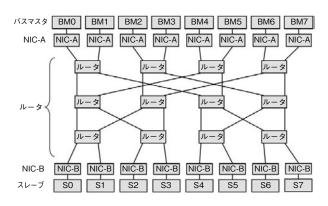

NoCは、ルータを用いてネットワーク型のバスを構築してパケット交換方式で通信を行う技術である。第2図に一般的なNoCの構成例を示す。

バスマスタは、NIC(Network Interface Controller)を 介してルータと接続される。NICはデータのパケット化、 およびパケットからデータのデパケット化を行う。また、 パケットには、宛先(あてさき)を識別するアドレスが 記述され、各ルータはアドレスに基づき経路制御を行う ことで、バスマスタからスレーブにデータが転送される。 NoC構造の導入により、例えば以下のメリットが生まれる[1]。

第2図 一般的なNoCの構成例

Fig. 2 Example of structure of general NoC

#### [1] バスマスタの配置制約の緩和

ルータは、複数のバスを集約する役割と、バスバッファ (長配線を分割するリピータ)の役割を担うため、ルータ配置の変更により、バスマスタの配置制約の緩和を実 現できる。また、ルータでの経路制御により、物理的な バスマスタ配置に依存せず、ルータの配置と宛先を変更 することで柔軟な伝送経路の設定が可能となるため、バ スマスタの配置制約の緩和を実現できる。

#### [2] バス配線集中の抑制

NICでのデータのパケット化により、アドレスと制御情報を、データ信号線を使って伝送ができるため、集中型バスに比べてバス幅を小さくできる。また、ルータで複数バスの集約も可能なため、バス配線集中の抑制が期待できる。さらに、NICでのバスプロトコル変換により、バスプロトコルに依存しないバス伝送を実現することで、バス配線を増やさずに多様なバスプロトコルへの対応が容易である。

上記のNoC構造のメリットを生かしたさまざまなNoC が提案されている[1]. 今後, バスのトラヒックが増大すると, 高いバス動作周波数で動作させる必要があるため, 以下の課題が生じる.

## (1) バスの消費電力の増大

一般に、CMOS(Complementary Metal Oxide Semiconductor) 回路の消費電力は動作周波数に比例し、電源電圧の2乗 に比例するため、バス動作周波数の増大に応じてバスの 消費電力も増大する。また、従来技術のNoCでは、パケットを処理していない状態(もしくは、バスの伝送負荷が 低い状態)を検出してルータへの電力供給を抑制することでバスの省電力化を図るため[2]、高負荷時の省電力 化には適用できない。

## (2) 実装面積の増大

バス動作周波数が高くなるほど、高速に動作できる駆動能力の高い素子が必要になり、回路もパイプライン段数を深くする必要があるため実装面積は大きくなる.

## (3) レイアウト設計の難化

バス動作周波数が高くなるとプロセスや周波数による 制約が増加し、長配線が厳しくなるため半導体集積回路 のレイアウト設計が難しくなる. 本稿では、伝送負荷が高い状態でも、バスの伝送負荷を複数の宛先に分散してバス動作周波数を低く保つ伝送負荷均一化方式について述べる。この方式により、トラヒック量が増大しても、バス動作周波数を上げずに低いバス動作周波数のままで伝送性能を向上できる宛先分散型のNoCを実現する。宛先分散型のNoCの実現により、バス動作周波数を低く保つことで、バスの省電力化、バスの実装面積の抑制、およびレイアウト設計の容易化が期待できる。

## 3. NoC構造の課題

NoC構造の導入により生じる課題について述べる. NoCでは複数のバスマスタ間で伝送経路を共有するため, 伝送負荷集中が発生しやすくNoC全体の伝送性能の低下が生じやすい. このため, 伝送性能の低下を防ぐためには, バス動作周波数を増加させる必要がある.

従来研究では、伝送負荷集中の回避方法として、ルータの伝送負荷に応じて伝送経路を動的に決定する動的ルーティングが提案されている[3]. 動的ルーティングは伝送負荷の少ない伝送経路へトラヒックを迂回(うかい)させることで伝送負荷集中の回避を行う. しかし、選択される伝送経路がルータの伝送負荷に応じて動的に変化するため、利用できる伝送帯域の事前見積もりは難しく、バス動作周波数が過剰に見積もられる. また、ルータの実装も複雑になり実装面積が増大する.

また、トラヒックの送信時に動的に伝送帯域を予約する方式が提案されている[4]. 事前に伝送帯域を予約したトラヒックのみを送信することで、伝送負荷集中を防ぐ. しかし、トラヒック数の増加に対するスケーラビリティが低く、大規模な半導体集積回路の実現が難しい.

## 4. 宛先を分散できるバスモデルの採用

本稿では、「宛先を分散できるバスモデル」と「自律分散的なバス伝送の負荷分散処理」により、伝送負荷集中を防ぐことで、トラヒック量が増大しても、バス動作周波数を上げずに低いバス動作周波数のままで伝送性能を向上できる宛先分散型のNoCを実現する。これにより、NoC構造の課題である伝送負荷集中の課題も解決できることを示す。

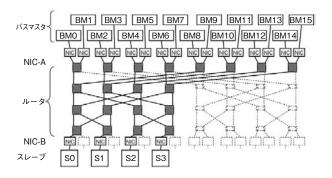

宛先を分散できるバスモデル(例:バタフライ,メッシュ)を対象とし、バスモデルとして、バタフライ網を採用した(第3図)、バタフライ網を採用する理由は、①各バスマスタは、任意のスレーブの選択が可能である。②ルーティングが固定、かつバスマスタとスレーブ間の

第3図 バタフライ網の例

Fig. 3 Example of butterfly networks

距離が一定であるため、利用できる伝送帯域や伝送遅延の事前見積もりが容易である。③往路と復路が独立しているため、往路と復路のトラヒックの干渉で伝送負荷集中が発生しない。④ルータのポート数が少なく、ルータでのトラヒック干渉の影響と実装面積の抑制が容易であるからである。

バスマスタ(BM0~BM7)はプロセッサやDSPなどの処理ノードであり、スレーブ( $SO \sim S7$ )は共有メモリーや、共通のI/O(Input/Output)である。バスマスタ側のNICをNIC-A、スレーブ側のNICをNIC-Bと定義する。

以上のバタフライ網の構成により、各バスマスタはスレーブの負荷に応じて任意のスレーブの選択が可能となり、バスマスタ間でスレーブへのアクセス負荷の分散を実現できる。なお、バタフライ網だけではなくメッシュなどの各バスマスタから任意でスレーブを選択できる網で実現してもよい。

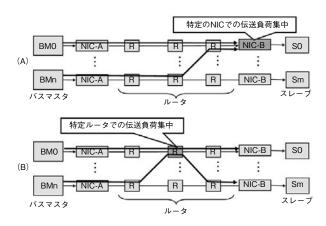

## 5. 伝送負荷均一化方式

利用帯域の事前見積もりを可能とし、スケーラビリティの高いトラヒック制御方式の実現を目指し、NoCで発生する伝送負荷集中の要因として、2種類の原因に着目した(第4図).1つ目の原因は、特定のスレーブへの伝送負荷集中で生じる「特定のNICでの伝送負荷集中」であり(第4図(A))、2つ目の原因は、特定のルータにおいて、一部のスレーブへの伝送が優先的に伝送されることで生じる「特定のルータでの伝送負荷集中」である(第4図(B)).2種類の伝送負荷集中の課題を解決するために、NICやルータの自律分散的な伝送負荷均一化処理により、バス全体の伝送負荷を均一に保ち、バス動作周波数の増大を抑制する伝送負荷均一化方式について述べる[5].

この方式により、ハードウェアの実装面積を抑えなが

第4図 伝送負荷集中の原因

Fig. 4 Causes of concentration of transmission loads

ら、伝送帯域を最大化する伝送負荷均一化方式の実現を 目指し、バス動作周波数の増大を抑制できる。

## 5.1 NIC間の伝送負荷均一化

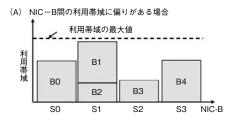

「特定のNICでの伝送負荷集中」の課題例を第5図(A)に示す。想定するネットワークモデルでは、バスマスタはトラヒックの送信前にスレーブを1つ選択してトラヒックを送信する。スレーブの選択を Round-Robin 方式で実現した場合、バスマスタごとに送信レートが異なるためスレーブの選択の結果によっては、NIC-B間で利用帯域に偏りが発生し、特定のNICで伝送負荷集中が生じる。この偏りが大きいほど利用帯域の最大値が増大する(第5図(A))。

これに対し、NIC-B間で利用帯域の均一な状態を維持できれば、利用帯域の最大値が低く抑えられ、特定のNICでの伝送負荷集中の課題を解決できる(第5図(B)).

第5図 NIC間の伝送負荷均一化の効果

Fig. 5 Effect of load equalization among NICs

本方式はNIC-Bの利用帯域に基づき、NIC-B間での利用 帯域が均一になるようにスレーブを選択する.

具体的には、①NIC-Aはトラヒックの送信開始時に、各NIC-Bに利用帯域を問い合わせる。②NIC-Bは利用帯域を問い合わせ元のNIC-Aに通知する。③NIC-Aは通知された利用帯域が最も小さいNIC-Bと接続するスレーブを宛先として選択しトラヒックを送信する。以上の手順で、NIC-B間での伝送負荷均一化を実現する。

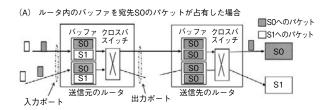

## 5.2 ルータ内の伝送負荷均一化

「特定ルータでの伝送負荷集中」の課題例を, 第6図 (A) に示す. ルータは入力ポートと出力ポートを2個ずつ備え, クロスバ・スイッチにより入力ポートと出力ポートの接続を切り替える. 各入力ポートは複数のバッファを備える. 第6図の例では, 入力ポートごとに2つのバッファを備える. 送信元のルータは, 送信先のルータへのデータ伝送前に, 送信先のルータのバッファを確保してパケットを転送する.

送信時刻でバッファの確保を行う従来方式 (Age-Based 方式[6]) では、ルータに同一スレーブへのパケット (例 えば、スレーブSO) が連続して届いた場合、送信先のルータのバッファがすべてスレーブSOのパケットで占有される. これにより、スレーブS1のパケットを中継できず、ルータでの伝送負荷集中が発生する (第6図 (A)).

本方式は、宛先のスレーブを区別してバッファの割り当てを行う。これによりスレーブS0とスレーブS1の宛先のパケットの同時送信が可能となり、ルータ内での伝送負荷集中を抑制できる(第6図(B)).

具体的には、ルータはスレーブごとにパケットの送信順序を管理し、異なるスレーブのパケットが優先的に送信先のルータのバッファを確保できるようにする.

第6図 ルータ内の伝送負荷均一化の効果

Fig. 6 Effect of load equalization in router

## 6. 評価結果

Verilog-HDL(Hardware Description Language)を用いたハードウェア実装による伝送負荷均一化方式の評価結果を示す.以下で、評価条件、および伝送性能、実装面積、バス幅の各評価結果について述べる.

#### 6.1 評価条件

## [1] バスモデル

評価対象のバスモデルとして4段のバタフライ網を用いた. 16個のバスマスタと4個のスレーブ, および20個のルータを, 第7図の形態で接続した. データ転送のバス幅は64 bitとした.

#### [2] トラヒックモデル

パケット長は18 flit (ヘッダ長2 flit, 1 flit はバスが1 サイクルで送信できるデータ量). バスマスタごとにパケットの送信間隔をガウス分布で変動させることでトラヒックの送信レートが変動するようにし、各バスマスタから4本(低レート3本、高レート1本)のトラヒックを送信した.

なお、現実的な評価を行うためにトラヒック間の送信 レートに差を設けることで送信レートの偏りを設けた.

第7図 評価対象のバスモデル Fig. 7 Evaluated bus model

## 6.2 伝送性能とバス動作周波数の評価

伝送負荷均一化方式の伝送性能の評価結果を,第1表

#### 第1表 伝送性能の比較

Table 1 Comparison of transmission performance

|     | 伝送負荷均一化          | トラヒック間の<br>送信レート比率 | 平均スループ<br>[flit/cycl<br>従来方式 |      |

|-----|------------------|--------------------|------------------------------|------|

| 評価1 | NIC間のみ           | 2倍                 | 0.62                         | 0.94 |

|     |                  | 10倍                | 0.33                         | 0.93 |

| 評価2 | ルータ内のみ           | 1倍                 | 0.8                          | 0.9  |

| 評価3 | NIC間とルータ<br>内の両方 | 10倍                | 0.33                         | 0.98 |

に示す. バス動作周波数は160 MHzとし, 各バスマスタからのトラヒックの送信レートを段階的に増やして, 平均スループットの最大値を計測した.

比較のために、従来方式として、スレーブの選択をRound-Robin 方式で、ルータでのバッファの割り当てをAge-Based 方式で行った場合とを比較した. なお、低レートの平均スループットに対する高レートの平均スループットの比率が2倍と10倍の条件でハードウェア実装による性能評価を行った.

NIC間の伝送負荷均一化のみを適用した評価1では、トラヒック間の送信レートの差が2倍の条件で、平均スループットの最大値は、従来方式の 0.62 flit/cycle/slave から本方式の 0.94 flit/cycle/slave に改善された。また、送信レート差が10倍の条件では、平均スループットの最大値が従来方式の 0.33 flit/cycle/slave から、本方式 0.93 flit/cycle/slave に改善された.NIC間の負荷均一化方式では、送信レート差が大きくなるほどスループットの改善効果が高くなることが明らかになった.

ルータ内の伝送負荷均一化方式のみを適用した評価2では、一部のルータで伝送負荷集中が発生するように各バスマスタの送信先となるスレーブを事前決定した。その結果、平均スループットの最大値は従来方式の 0.8 flit/cycle/slave から、本方式の 0.9 flit/cycle/slave に改善された。ルータ内の伝送負荷均一化により、ルータの伝送性能を高められることが明らかになった。

NIC間とルータ内の伝送負荷均一化方式の両方を適用した評価3では、平均スループットの最大値は、従来方式の 0.33 flit/cycle/slave に対して、本方式では 0.98 flit/cycle/slave に改善された.

以上の結果から、本方式により、NoC構造の課題である複数のバスマスタ間での伝送経路の共有で生じる伝送性能の低下の課題を解決できることが確認できた。また、バス動作周波数を上げずに、低いバス動作周波数のままで伝送性能を3倍に向上できることが明らかになった。なお、従来方式で、本方式と同じ伝送性能を確保するためにはバス動作周波数を少なくとも3倍(480 MHz)に高める必要がある。

## 6.3 実装面積の評価

Verilog-HDLを用いたハードウェア実装を行い、NICとルータのゲート数を算出した。また、バス動作周波数は160 MHzとして、バス全体と1個当たりのNICおよびルータについて実装面積と、その中で本機能が占める実装面積と面積割合を求めた(第2表)。

バス全体の実装面積 (第7図の評価対象のバスモデル を構成する20個のルータと20個のNICの合計面積) は

第2表 実装面積の比較

Table 2 Comparison of implemented area

|            |       | 実装面積<br>[kgate] | 本機能が占める<br>実装面積<br>[ k gate ] | 本機能が占める<br>面積割合<br>[%] |

|------------|-------|-----------------|-------------------------------|------------------------|

| バス全体       |       | 923.8           | 87.9                          | 9.5                    |

| NIC(1個当たり) |       | 16.3            | 2.8                           | 17.2                   |

|            | NIC-A | 15.5            | 2.7                           | 17.4                   |

|            | NIC-B | 19.1            | 3.1                           | 16.2                   |

| ルータ(1個当たり) |       | 29.9            | 1.6                           | 5.3                    |

923.8 k gate であり、各構成において本機能が占める面積割合は、バス全体で 9.5 %、NIC 17.2 %(NIC-A 17.4 %、NIC-B 16.2 %)、ルータ 5.3 %である.

ところで、ルータの伝送性能は、バッファを増やすことでも改善が可能である[7]. Age-Based 方式のルータのバッファ数を2個から4個に倍増させて、伝送性能と実装面積について、本方式と比較した(第3表).

第3表 ルータの実装面積と伝送性能の比較

Table 3 Comparison between implemented area and transmission performance for routers

|             | バ <sub>ツ</sub> ファ<br>数 | 実装面積<br>[kgate] | ①に対する<br>面積増加率<br>[%] | 平均スループットの<br>最大値<br>[flit/cycle/slave] |

|-------------|------------------------|-----------------|-----------------------|----------------------------------------|

| ① Age-Based | 2個                     | 28.3            | 0.0                   | 0.81                                   |

| ② 本方式       | 2個                     | 29.9            | 5.7                   | 0.91                                   |

| ③ Age-Based | 4個                     | 54.2            | 91.4                  | 0.98                                   |

Age-Based 方式のルータでは、バッファを倍増することで、平均スループットの最大値を 0.81 flit/cycle/slave から 0.98 flit/cycle/slave まで向上できるが、実装 面積が 91.4 %増加する。これに対し、本方式では、実 装面積の 5.7 %増加だけで、平均スループットの最大値を 0.91 flit/cycle/slave まで向上できる。本方式により、実装面積の増加を抑えた伝送性能向上が可能となる。

#### 6.4 バス幅の評価

標準的なAMBA AXI (注) (Advanced Microcontroller Bus Architecture Advanced eXtensible Interface) ver.1.0と、最小信号構成の条件でバス幅の比較を行った。NICでのデータのパケット化により、アドレスと制御情報を、データ信号線を使って伝送することで、AMBAに比べてバス幅を小さく実現できた。具体的には、AXI (268 bit) に対して、NoCでは2/3 (174 bit) のバス幅を実現できた。

また、ルータでの複数バスの集約とNICでのバスプロトコル変換により、バスプロトコルに依存しないバス伝

<sup>(</sup>注) AMBA, AXIは, ARM Limited の登録商標

特

送を実現することで、バス配線集中の抑制が期待できる.

AXI (最小信号構成)

送受信のデータ信号線: 128 bit アドレス信号線: 64 bit 制御信号線: 76 bit 合計: 268 bit

#### NoC

送受信のデータ信号線: 128 bit 制御信号線: 46 bit 合計: 174 bit

# 7. まとめ

本稿では、半導体集積回路おけるバスマスタの配置制約、バス配線の集中やバスの種類の多様化、トラヒック量の増加によるバス動作周波数の増大の課題に対し、バスをネットワーク化(NoCの導入)することで緩和できることを示した。なお、バス動作周波数を低く保つことで、バスの省電力化、バスの実装面積の抑制、およびレイアウト設計の容易化が期待できる。

宛先を分散できるバスモデルとしてバタフライ網を採用し、伝送負荷集中を抑制する伝送負荷均一化方法により実現した。実現方法としては、NICとルータでの自律分散的な伝送負荷均一化処理により、各NICやルータ間の伝送負荷を均一に保つことで、トラヒック量の増加による伝送負荷集中を抑制した。また、ハードウェア実証により、トラヒック量が増加しても、本方式は、バス動作周波数を上げずに低いバス動作周波数のままで伝送性能を向上できることを示した。本方式では次の特徴をもつ

- バス動作周波数を低く保ちつつ, 従来方式に対して バスの平均スループットの最大値を3倍向上可能

- ハードウェアの実装面積を抑えた伝送性能向上が可能

- ハードウェア設計時に必要な伝送帯域の見積もりが 容易

- トラヒック数の増加に対するスケーラビリティが高く、大規模な半導体集積回路を構築が容易

スケーラビリティの評価は今後の課題である. 具体的には、さらに規模の大きなバタフライ網においてスレーブ数やスレーブの配置を加味した性能評価[6]や、メッシュ網などのほかのトポロジーでの性能評価をバタフライ網と比較して行う予定である.

#### 参考文献

- [1] T. Bjerregaard et al., "A survey of research and practices of network-on-chip," ACM Computing Surveys, vol.38, no.1, pp.1-51, 2006.

- [2] 松谷宏紀 他, "CMPにおけるオンチップルータの細粒度パワーゲーティングの評価," 情報処理学会論文誌.コンピューティングシステム, vol.3, no.3, pp.100-112, 2010.

- [3] L. Tedesco et al, "A path-load based adaptive routing algorithm for networks-on-chip," Proceedings of the 22nd Annual Symposium on Integrated Circuits and System Design: Chip on the Dunes, pp.1-6, 2009.

- [4] K. Goossens et al., "AEthereal network on chip: concepts, architectures, and implementations," Design & Test of Computers, IEEE, vol.22, no.5, pp.414-421, 2005.

- [5] 吉田篤 他, "分散型バスにおける伝送負荷均一化方式の提案," 情報処理学会研究報告 計算機アーキテクチャ研究会報告, vol.2011, no.7, pp.1-8, 2011.

- [6] D. Abts et al, "Age-based packet arbitration in large-radix k-ary n-cubes," Proceedings of the 2007 ACM/IEEE conference on Supercomputing, pp.1-11, 2007.

- [7] W. J. Dally, "Virtual-channel flow control," IEEE Transactions on Parallel and Distributed Systems, vol.3, no.2, pp.194-205, 1992

## 執筆者紹介

吉田 篤 Atsushi Yoshida 先端技術研究所 Advanced Technology Research Labs.

石井 友規 Tomoki Ishii 先端技術研究所 Advanced Technology Research Labs.

山口 孝雄 Takao Yamaguchi 先端技術研究所 Advanced Technology Research Labs. 工学博士