# 当社の半導体パッケージ技術展望

Technology Trends in Semiconductor Packages

中 村 嘉 文\*

Yoshifumi Nakamura

半導体の拡散プロセスの微細化が進む中で、そのチップに対応したパッケージング技術も更なる進化が要求されている。また、高機能化したセット商品の特性を生かすための位置づけとしてもパッケージへの要求は増加している。これらを実現するための筆者らが有するパッケージの要素技術とパッケージ開発の取り組み、および今後の開発の方向性について報告する。

With the advances in miniaturization of the semiconductor diffusion process, additional progress in packaging technology corresponding to individual chips is needed. In addition, the requirements for packages are increasing to utilize the characteristics of high-function-set products.

We report the approaches to develop fundamental package technologies and package types as well as future technology trends to successfully meet these demands.

# 1. 半導体パッケージを取り巻く状況

90年代は、モバイル機器の高機能化と小型化に伴い、高 集積や高機能の半導体が要望されてきた。その要望を実 現するために、半導体の拡散プロセスにおいては微細化 により高集積化を進展させてきた。半導体パッケージに おいては小型化が開発の主戦場となりCSP(Chip Size Package)が進展した時代であった。

しかし、21世紀になりシステムLSIの大規模化による開発の複雑化、拡散プロセスのさらなる微細化、微細接合の複雑化により、もはやチップ設計の段階からパッケージ設計との協調なくしては商品が成り立たなくなっている。さらに、自動車のエレクトニクス化の増加に伴い高信頼性を有する車載仕様の要望も大きくなり、またさまざまなセンサ用の半導体においては高機能なパッケージが必要とされてきている。半導体各社の差別化も"拡散プロセスの技術力・製造力と投資"を中心としたものから"システムとしての半導体の設計資産力"と"高機能半導体の特性を最大限に生かすパッケージ設計力"に移行しつつある。これらを結びつけるソリューションを提供するところがパッケージ開発の重要な要点となる。

#### 2. 当社のパッケージ戦略

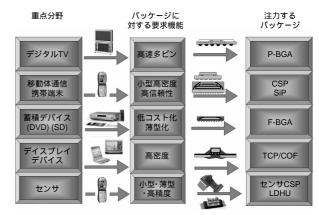

当社では,**第1図**に示すようにパッケージが高速化や小型化に大きく関与すべき情報家電における重点商品分野として,デジタルTV,移動体通信・携帯端末,蓄積デバイス(DVD),ディスプレイデバイス,コアカメラや光ピ

P-BGA : Plastic Ball Grid Array F-BGA : Fine pitch Ball Grid Array COF : Chip on Film SiP: System in Package TCP: Tape Carrier Package LDHU: Laser Detector Hologram Unit

第1図 半導体パッケージ戦略

Fig. 1 Strategy of semiconductor package

ックアップなどの,センサを主体とした5つを重点分野として位置づける。その中で,パッケージとして新しい形のソリューションの提供が求められる分野は,移動体通信・携帯端末分野である。この分野においては,エリアアレイ状に外部接続端子を有するCSPやBGA(Ball Grid Array)が開発の主体になるが,SiPの提供によるシステムの構築,車載仕様の高信頼性(EMI(Electro Magnetic Interference)対策,高二次実装信頼性)化を加味する必要もある。

このCSPやBGAにおいては、ピン数領域別に異なるテクノロジーを適用したパッケージを有することにより、各用途での最適な形態を実現している。リードフレームを利用したタイプでは、移動体通信向けの小型高密度のローコスト版としてI(Lead frame)CSP、設計の自由度の高い基板タイプは高速多ピン用としてP-BGAで150ピン~860ピンを網羅し、小型高密度のローコストの多ピン向けと

<sup>\*</sup> セミコンダクター社 生産本部 Corporate Manufacturing Div., Semiconductor Company

してF-BGAを適用している。CSPやBGAを有する最大の理由は,多ピン領域における1ピン当たりのコストがQFP (Quad Flat Package)では急激に増加することと比較して,CSPやBGAのようなエリアアレイパッケージではコストが緩やかな増加になることにある。したがって,今後もエリアアレイタイプを多ピン領域に積極的に採用していく。

これまで、当社はセラミック、リードフレームという 材料でCSPの展開を行ってきたが、2005年度にこの方針の 再検討を行い、車載対応などにおける二次実装信頼性要 求の困難化に対応するために、樹脂基板材料を採用した F-BGAを開発し、その展開を推進している。

## 3. 半導体パッケージの要素技術の進展

上記の重点分野のパッケージ群を実現するための,共通的な要素技術とカスタム的な技術とについて説明する。

#### 3.1 半導体チップの接合技術

パッケージング技術の重要要素である半導体チップの 接合技術について,長い間 基幹技術として使用されてい るワイヤボンディングと,高機能小型化には欠かすこと のできなくなったフリップチップボンディングについて 以下に示す。

まず,ワイヤボンディングの技術トレンドを,**第2図**に示す。

多ピンへの対応として

ペリフェラル (ストレート)配置でのパッドの狭ピッチ化による方法

多段千鳥配置による広いパッドピッチでありながら見

|     |        | ~ 2006年 | 2007年  | 2008年 | 2009年 |

|-----|--------|---------|--------|-------|-------|

| ピッチ | ペリフェラル | 55 µm   | 50 µm  | 同左    | 同左    |

|     | 千鳥     | 40 µm   | 35 µm  | 同左    | 26 µm |

|     |        | 2段      | 2段     |       | 3段    |

| ワイヤ | ループ高さ  | 120 µm  | 80 µm  | 70 μm | 同左    |

|     | (min.) |         |        |       |       |

|     | ワイヤ長   | 5.0 mm  | 6.0 mm | 同左    | 同左    |

|     | (max.) |         |        |       |       |

低ループワイヤ

多段ボンディング

第2図 ワイヤボンディングロードマップ Fig. 2 Roadmap of wire bonding technique

#### かけ上のピッチを小さくする方法

とを開発し、量産化している。多段千鳥配置ではワイヤが重なり合い複雑な構造となるため、ワイヤループ形状が重要なファクタとなる。さらには、樹脂モールドの影響も受けやすく、モールドする樹脂材料の選択やその形成条件も重要なファクタとなる。狭ピッチを実現するため、ワイヤ径や樹脂封入条件などワイヤボンディングと樹脂モールドとの相互間での最適化を図っている。

成熟していると考えられているワイヤボンディング工法も,チップの多ピン化やパッケージの薄型化に適応すべくパッドの狭ピッチ化,長ワイヤ化や低ループ化を実現することで進化し続けている。

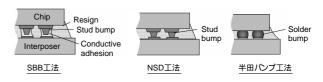

次に,フリップチップ実装工法の技術トレンドを,**第3** 図に示す。当社では,導電性接着剤を使用したSBB(Stud Bump Bonding)接続から,導電接着剤を有さない金-金接合のNSD TM(Non conductive adhesive Stud bump Direct interconnection 1) への工法の進展により,狭ピッチ接合を実現させてきた。しかしながら,更なる多ピン,高機能,高速対応の実現のためには,パッド配置に限界のあるペリフェラル接続からエリア状の接続が必須となる。現在,エリア接続工法として,低応力タイプの半田バンプ接合技術を民生向け用途として技術開発中である。

|     |        | ~ 2006年 | 2007年 | 2008年 | 2009年  |

|-----|--------|---------|-------|-------|--------|

| SBB | ペリフェラル | 80 µm   | 同左    | 同左    | 同左     |

|     | 千 鳥    | 50 µm   | 同左    | 同左    | 同左     |

| NSD | ペリフェラル | 80 µm   | 同左    | 同左    | 同左     |

|     | 千 鳥    | 50 µm   | 同左    | 40 µm | 同左     |

| 半田  | T 11 7 | -       | •     | •     | 180 µm |

| バンプ | エリア    |         |       |       |        |

第3図 フリップチップ接続工法のロードマップ Fig. 3 Roadmap of flip chip bonding technique

#### 3.2 SiP (System in Package)への対応

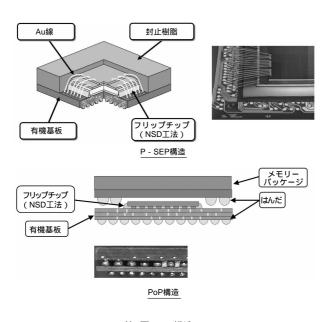

さまざまな種類の半導体の設計資産を生かし,機能をパッケージに取り込むための形態として,SiPは最適なソリューションである。当社では,生産性やコストなどを考慮してSiPにMCM(Multi Chip Module),SEP(System Embedded Package TM),PoP(Package on Package)の3タイプを採用している。SEPは,機能の異なるチップをスタック化してパッケージングする方法であり,高機能小型化が進む携帯電話向けに2001年適用以来,大幅に増加して

いる。QFPにチップを2枚重ねてモールドを行うQ-SEP (QFP type-SEP)は,主にメモリーとのSiP化であり,今後SiPの(品種数/数量)主流になる。第4図に示すような最下段のチップをフリップチップ実装しSiP化を行うP (Plastic )SEP <sup>2)</sup>は,多ピン向きである。このタイプにおいては,インターポーザーの設計の自由度が高い。また,中ピン領域に対し,小型とコストに対応するために,F-BGAタイプのSiPであるF-SEP (F-BGA type SEP)もラインナップしている。低背が要望される用途と小面積が要望される用途とで,MCMとSEPは使い分けている。

PoPは,SiPにおいて大きな課題になる大容量のメモリー品質保証に対応するために開発し,2006年より量産している。

また,高機能多機能化が要求される用途では,チップの接合形態としては多ピン化に有利で高速伝送性も優れるエリア接続を基軸としたFC(Flip Chip) BGAや,FC(Flip Chip) PoPも開発中である。

第4図 SiP構造 Fig. 4 SiP structure

# 4. 今後の開発の方向性

今後も進展が進む電子機器の高機能多機能と小型化に 適応するために,パッケージ技術開発としては,重点分 野への取り組みと並行して,

- (1)開発期間短縮の目的のためには、「機能単位の設計データの共有化」を最大限に活用しつつ、多様化するニーズに対応する高機能化に対しては、新たな実装技術・モールドパッケージング技術と半導体製造プロセス技術とを高度にインテグレートしたコンカレント設計思想で差別化を図る。

- (2)今後も需要が増加すると予測されるカーエレクトロニクスへの対応として,AV周辺技術の強みを生かしつつ車載品質に適合した材料や実装形態の開発を進める。

- (3)多様な用途が考えられるイメージセンサにおいては, 小型化への対応と,センサとして必須の低ダストや 高組立精度を実現する構造や生産プロセスの確立を さらに進める。

これまで、パッケージは半導体の付加価値を生み出す 大きな要因とは考えられてこなかった。しかしながら、今 後は上手な半導体の設計資産の活用方法、セットに最適 のパッケージ提案と設計提案や生産方法提案が差別化の 重要な要因になってくる。パッケージの生産の場につい ても、コスト重視の汎用パッケージと、ソリューション を提供する高付加価値パッケージとに切り分けて考えて いく必要がある。

## 参考文献

- 1) 西田一人 他: 圧接構造フリップチップ実装技術を用いた積層パッケージング技術の開発 エレクトロニクス実装学会誌 5,No.7,pp.693-700 (2002).

- 吉村義一 他:スタックド半導体パッケージ(P-SEP)対応 微細接合技術 Matsushita Tech. Journal 52,No.2,pp.77-80 (2006).