# 高精度TCADを用いた ばらつき考慮プロセス設計

Semiconductor Process Design for Variability Using Highly Accurate TCAD

海本博之\* 栗本一 実\*

Hiroyuki Umimoto Kazumi Kurimoto

高精度TCAD(Technology Computer Aided Design)技術を用いて,半導体プロセス要素・モジュール・デバイス・セルを階層化して紐(ひも)付けする手法を開発した。この手法により微細化に起因するばらつきを考慮したロバスト設計を可能にし,65/45 nm CMOS(Complementary Metal Oxide Semiconductor)プロセスの早期量産化を実現した。

We have developed a new method to stratify and make connections of process elements, modules, devices and cells in semiconductors based on high-accuracy Technology Computer Aided Design (TCAD). This method allows robust design for variability in miniaturization and realized an accelerated schedule for mass production of 65/45 nm Complementary Metal Oxide Semiconductor (CMOS) process.

#### 1. TCAD技術の概要

TCADは,スタンフォード大学のDutton教授が命名した 半導体プロセス・デバイス・回路シミュレーション技術 の総称である<sup>1)</sup>。種々の物理モデルをベースに記述され る連立偏微分方程式などを数値的に解いて,半導体プロ セスのシリコン基板中のn型/p型不純物分布,電流電圧 特性などのデバイス性能およびセル性能を予測する。

TCADの予測精度が向上し計算機上で仮想試作が可能になれば,プロセス試作回数の大幅削減が可能となる。また,65 nm~45 nmと微細化が進むと加工ばらつきや不純物分布ゆらぎが増加するため,ばらつきを考慮した設計を実現させ,性能・歩留まり・品質の向上を図ることが不可欠となる<sup>2)</sup>。

# 2. 階層的アプローチと高精度な紐付け

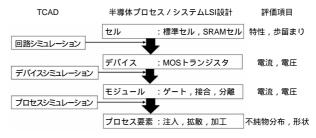

システムLSI設計とプロセス開発の垂直統合メリットを生かしたコンカレント開発を実現させるため,セルレベルからデバイス,モジュール,プロセス要素レベルまでの階層的アプローチを試みた(第1図)。

上位階層の特性と下位階層のプロセス条件を,TCADで高精度に紐付け,各階層に要求されるスペック(基準値,上限/下限値)をプロセス試作前に明確化し,コンカレント開発とロバスト設計を同時に実現した。実現の鍵となったのは,主にプロセス要素レベルでの高精度なシミュレーションを実現するモデリング技術開発である。

\* セミコンダクター社 生産本部 Corporate Manufacturing Div., Semiconductor Company

SRAM : Static Random Access Memory MOS : Metal Oxide Semiconductor

第1図 TCADで紐付けられた階層的アプローチ Fig. 1 Hierarchical approach linked by TCAD

## 2.1 プロセス要素モデリング

不純物分布を決定するプロセス要素は,主にイオン注入と熱拡散工程である。注入機で加速された不純物イオンがシリコン格子と衝突し点欠陥を生成しながらシリコン基板内に分布する現象を,運動方程式で定式化しモンテカル口法で求めた。また,熱拡散は不純物と点欠陥のペアやクラスタ生成を考慮した連立移流拡散方程式を連続体的に解き,拡散後の不純物分布を広範囲なプロセス条件で再現するようにした。また,KMC(kinetic Monte Carlo)法を用いて,不純物・点欠陥反応や(311)欠陥や転移ループなどの欠陥生成消滅を原子レベルで予測し,不純物の熱拡散予測精度の向上を図った³)。一方,エッチングやデポジション工程で形成されるトランジスタのゲートやサイドウォール形状は,物理モデル化が難しいため,実物の形状を直接取り込み,デバイス特性予測精度の向上を図った。

#### 2.2 モジュール・デバイスモデリング

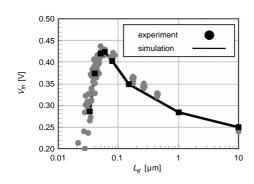

不純物分布の高精度シミュレーションの実現により,モジュールやデバイス特性のプロセス条件変動や形状依存性をデバイスシミュレーションで紐付けすることを可能とした。精度検証の例として,45 nm世代のnMOS(negative-

—— 特 集 1

channel Metal Oxide Semiconductor)トランジスタの閾値(しきいち)電圧のゲート長依存性を示す(第2図)。

第2図 閾値電圧 $V_{th}$ のゲート長 $L_g$ 依存性 Fig. 2 Short channel effects of nMOSFETs

### 3. ばらつき考慮プロセス設計

高精度化したTCADを用いて、デバイスやセルの特性ばらつきを予測した。所望のワースト性能や動作マージンが得られるように、各階層に立ち戻り紐付けされたプロセス管理指標や、デバイス動作条件を最適化することで、ばらつきを考慮したロバスト設計を実現した。

#### 3.1 プロセス・デバイス設計への応用

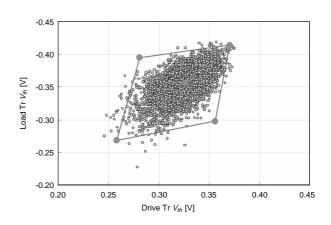

最初に,モジュールやデバイス特性の要素プロセス条件や形状に関する感度解析を行った。次に,主要な感度をもつプロセス条件因子を用いて2次多項式を用いた応答曲面関数を生成した。最後に,応答曲面関数を用いてばらつき解析を実行してデバイス特性の頻度分布を求めた(第3図)。

加工ばらつき抑制対策やトランジスタ最適化設計により,加工寸法やトランジスタ特性がともに規格限度内で

第3図 Driveトランジスタ閾値電圧 $V_{th}$ のばらつき Fig. 3 Variability of  $V_{th}$  for SRAM drive transistor

生産できる工程能力指数Cp, Cpkを1.33以上にする設計を 実現した。

#### 3.2 SRAMセル設計への応用

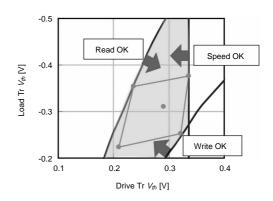

SRAMの動作マージンは,加工ばらつきと不純物分布ゆらぎの両者を考慮して設計した。最初に,加工ばらつきによりSRAM セルのDrive/Loadトランジスタの閾値電圧V<sub>th</sub>がワーストケースでどのようにばらつくかを求めた(第4図)

第4図 SRAMセルトランジスタの閾値電圧コーナー解析 Fig. 4 Corner analysis of  $V_{th}$  for SRAM cell transistors

次に,トランジスタの電流電圧特性を回路モデル化し,微細トランジスタの閾値電圧が,不純物分布ゆらぎでゲート面積の平方根に反比例してばらつくこと4)を考慮して SRAMセルのワーストケース動作解析を行った。16 Mbit のSRAMセルでは5.4 の閾値ばらつき( 電源電圧の50%に相当)が生じる。書き込み可能,読み出し可能および読み出し速度スペック以上になる動作範囲に,第4図で求めた加工ばらつき起因の閾値コーナーが含まれるように,加工ばらつきの抑制,不純物ゆらぎの低減,トランジスタサイズ,SRAM駆動回路の最適化を行った(第5図)。

第5図 16 Mbit SRAM動作のワーストケース解析 Fig. 5 Worst case analysis of 16 Mbit SRAM operation

以上の取り組みにより,45 nm CMOSプロセスでは, 16 Mbit SRAMを高歩留まりで,しかも1回の試作で実現 できた。

# 4. TCAD技術動向と展望

次世代微細CMOSプロセス開発に向けて,原子レベルのモデリングによる精度向上が不可欠である。また,High-K絶縁膜などの新規材料やフィン構造などの3次元デバイス構造への対応と,アナログRF(Radio Frequency),高耐圧,イメージセンサなどの他分野への展開が必要である。

## 参考文献

- 1 ) R. W. Dutton, et al. : Technology CAD Computer Simulation of IC Processes and Devices. Kluwer Academic Publishers (1993).

- 2) 藤井英治 他: 65 nm CMOSプロセス技術 Matsushita Tech. Journal 52,No.1,pp.12-16 (2006).

- 3 ) T. Noda: Analysis of dopant diffusion and defect evolution during sub-millisecond non-melt laser annealing based on an atomistic kinetic monte carlo approach. Tech. Dig. IEDM2006 ,p.377 (2006).

- 4 ) P. A. Stolk, et al. : Modeling statistical dopant fluctuations in MOS transistors. IEEE Trans. Electron Devices 45,No.2,p.1960 (1967).